제품 카테고리

제품 태그

Fmuser 사이트

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> 아프리칸스어

- sq.fmuser.net -> 알바니아어

- ar.fmuser.net -> 아랍어

- hy.fmuser.net -> 아르메니아어

- az.fmuser.net -> 아제르바이잔 어

- eu.fmuser.net -> 바스크

- be.fmuser.net -> 벨로루시 어

- bg.fmuser.net -> 불가리아어

- ca.fmuser.net -> 카탈로니아 어

- zh-CN.fmuser.net -> 중국어 (간체)

- zh-TW.fmuser.net -> 중국어 (번체)

- hr.fmuser.net -> 크로아티아어

- cs.fmuser.net -> 체코

- da.fmuser.net -> 덴마크어

- nl.fmuser.net -> 네덜란드어

- et.fmuser.net -> 에스토니아어

- tl.fmuser.net -> 필리피노

- fi.fmuser.net -> 핀란드어

- fr.fmuser.net -> 프랑스어

- gl.fmuser.net -> 갈리시아어

- ka.fmuser.net -> 조지아 어

- de.fmuser.net -> 독일어

- el.fmuser.net -> 그리스

- ht.fmuser.net -> 아이티 크리올

- iw.fmuser.net -> 히브리어

- hi.fmuser.net -> 힌디어

- hu.fmuser.net 헝가리어

- is.fmuser.net -> 아이슬란드 어

- id.fmuser.net -> 인도네시아어

- ga.fmuser.net -> 아일랜드어

- it.fmuser.net -> 이탈리아어

- ja.fmuser.net -> 일본어

- ko.fmuser.net -> 한국어

- lv.fmuser.net -> 라트비아어

- lt.fmuser.net 리투아니아어

- mk.fmuser.net -> 마케도니아 어

- ms.fmuser.net -> 말레이어

- mt.fmuser.net -> 몰타어

- no.fmuser.net -> 노르웨이어

- fa.fmuser.net -> 페르시아어

- pl.fmuser.net -> 폴란드어

- pt.fmuser.net -> 포르투갈어

- ro.fmuser.net -> 루마니아어

- ru.fmuser.net -> 러시아어

- sr.fmuser.net -> 세르비아어

- sk.fmuser.net -> 슬로바키아어

- sl.fmuser.net -> 슬로베니아어

- es.fmuser.net -> 스페인어

- sw.fmuser.net -> 스와힐리

- sv.fmuser.net -> 스웨덴어

- th.fmuser.net -> 태국

- tr.fmuser.net -> 터키어

- uk.fmuser.net -> 우크라이나어

- ur.fmuser.net -> 우르두어

- vi.fmuser.net -> 베트남어

- cy.fmuser.net -> 웨일스 어

- yi.fmuser.net -> 이디시어

반감산기란 무엇인가 : 작동과 응용, K-MAP, NAND 게이트를 이용한 회로

Date:2021/10/18 21:55:58 Hits:

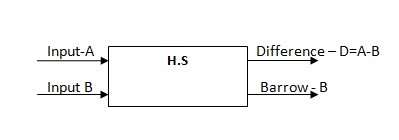

빛이나 소리와 같은 정보를 한 지점에서 다른 지점으로 처리하기 위해 아날로그 신호의 형태로 적절한 입력을 제공하여 아날로그 회로를 사용할 수 있습니다. 이 과정에서 입력 아날로그 신호에 의해 잡음이 포착될 가능성이 있으며 이는 출력 신호의 손실로 이어질 수 있습니다. 이는 입력 레벨에서 처리하는 입력이 무엇이든 출력 단계와 동일하지 않음을 의미합니다. 이를 극복하기 위해 디지털 회로가 구현됩니다. 논리 게이트로 디지털 회로를 설계할 수 있습니다. 논리 게이트는 입력을 기반으로 논리 연산을 수행하고 출력에 로우(논리 0=제로 전압) 또는 하이(로직 1=고전압)의 단일 비트만 제공하는 전자 회로입니다. 조합 회로는 둘 이상의 논리 게이트로 설계할 수 있습니다. 이 회로는 빠르고 시간에 구애받지 않으며 입력과 출력 사이에 피드백이 없습니다. 조합 회로는 산술 및 부울 연산에 유용합니다. 조합 회로의 가장 좋은 예는 반가산기, 전가산기, 반 감산기, 전 감산기, 다중화기, 역다중화기, 인코더 및 디코더입니다. 반 감산기란 무엇입니까? 위에서 말한 반 감산기는 조합 회로이며 이름 그대로 입력에서 두 비트를 빼는 데 사용됩니다. 여기서 감산기의 출력은 현재 입력에 전적으로 의존하며 이전 단계에 의존하지 않습니다. 반감산기 출력은 차이와 배로우입니다. 이는 빼기가 빼기보다 크면 차용 B = 1로 이동하거나 차용이 0으로 유지되는 B=XNUMX인 산술 뺄셈과 유사합니다. 더 잘 이해하기 위해 아래 표시된 진리표를 살펴보겠습니다.  half-subtractor-block-diagramThe truth Table반감산기 진리표는 입력 단계에서 적용되는 입력에 따른 출력 값을 보여줍니다. 진리표는 두 부분으로 나뉩니다. 왼쪽 부분은 입력 단계로 표시되고 오른쪽 부분은 출력 단계로 표시됩니다. 디지털 회로에서 입력 0과 입력 1은 로직 로우 및 로직 하이를 나타냅니다. 구성에 따라 로직 로우는 5 전압을 의미하고 로직 하이는 고전압(7V, 12V, 000010V 등)을 의미합니다. Inputs OutputsInput – AInput – Bdifference -DBarrow – B 1001111100 1Truth Table Explanation입력 A와 B가 1일 때 반감산기 D와 B의 출력도 0입니다. 입력 A가 높고 B가 0일 때 차이는 High 즉, 1이고 배 로우는 XNUMX입니다입력 A가 XNUMX이고 입력 B가 높으면 D와 B의 출력이 각각 높습니다. 두 입력이 모두 높으면 반감기의 출력은 모두 XNUMX입니다. 위의 진리표에서 우리는 할 수 있습니다 차이(D) 및 배로우(B)에 대한 방정식을 찾습니다. 차이-D에 대한 방정식: 입력 A=XNUMX, B=XNUMX 및 A=XNUMX, B=XNUMX일 때 차이는 높음입니다. 이 문장에서 D = AB'+A'B = A⊕B. D 방정식에 따르면 Ex-or 게이트를 나타냅니다. D=A⊕BE Barrow-B 방정식: Barro는 입력 A가 낮고 B가 높을 때만 높습니다. 이 지점에서 Barrow B에 대한 방정식은 다음과 같습니다. B= A'BB=A'B위의 차이 및 Barrow 방정식에서 K -MapK를 사용하여 반감산기 회로도를 설계할 수 있습니다. MapKarnaugh 맵은 부울 대수식을 단순화합니다. 반감기 회로의 경우. 이것은 모든 회로에 대한 부울 대수 방정식을 찾는 공식 방법입니다. K-map.K-Map for Difference(D) 및 Barrow(B)를 사용하여 반감산기 회로에 대한 부울 표현식을 해결해 보겠습니다.

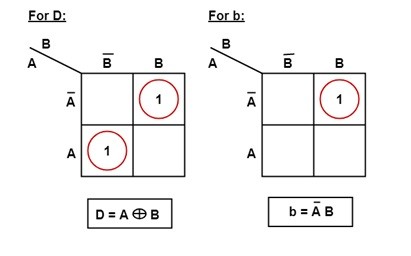

half-subtractor-block-diagramThe truth Table반감산기 진리표는 입력 단계에서 적용되는 입력에 따른 출력 값을 보여줍니다. 진리표는 두 부분으로 나뉩니다. 왼쪽 부분은 입력 단계로 표시되고 오른쪽 부분은 출력 단계로 표시됩니다. 디지털 회로에서 입력 0과 입력 1은 로직 로우 및 로직 하이를 나타냅니다. 구성에 따라 로직 로우는 5 전압을 의미하고 로직 하이는 고전압(7V, 12V, 000010V 등)을 의미합니다. Inputs OutputsInput – AInput – Bdifference -DBarrow – B 1001111100 1Truth Table Explanation입력 A와 B가 1일 때 반감산기 D와 B의 출력도 0입니다. 입력 A가 높고 B가 0일 때 차이는 High 즉, 1이고 배 로우는 XNUMX입니다입력 A가 XNUMX이고 입력 B가 높으면 D와 B의 출력이 각각 높습니다. 두 입력이 모두 높으면 반감기의 출력은 모두 XNUMX입니다. 위의 진리표에서 우리는 할 수 있습니다 차이(D) 및 배로우(B)에 대한 방정식을 찾습니다. 차이-D에 대한 방정식: 입력 A=XNUMX, B=XNUMX 및 A=XNUMX, B=XNUMX일 때 차이는 높음입니다. 이 문장에서 D = AB'+A'B = A⊕B. D 방정식에 따르면 Ex-or 게이트를 나타냅니다. D=A⊕BE Barrow-B 방정식: Barro는 입력 A가 낮고 B가 높을 때만 높습니다. 이 지점에서 Barrow B에 대한 방정식은 다음과 같습니다. B= A'BB=A'B위의 차이 및 Barrow 방정식에서 K -MapK를 사용하여 반감산기 회로도를 설계할 수 있습니다. MapKarnaugh 맵은 부울 대수식을 단순화합니다. 반감기 회로의 경우. 이것은 모든 회로에 대한 부울 대수 방정식을 찾는 공식 방법입니다. K-map.K-Map for Difference(D) 및 Barrow(B)를 사용하여 반감산기 회로에 대한 부울 표현식을 해결해 보겠습니다. 차이(D) 및 배로우(B)에 대한 K-맵에 따르면 첫 번째 함축 항목은 A'B이고 두 번째 함축 항목은 AB'입니다. 이 두 함축 방정식을 단순화하면 DD의 차이에 대한 단순화된 방정식을 얻을 수 있습니다. =A'B+AB'그러면 D=A⊕B입니다. 이 방정식은 단순히 Ex-OR 게이트를 나타냅니다. 배로우 B에 대한 단순화된 부울 표현식을 찾으려면 차이 D에 대해 따랐던 것과 동일한 프로세스를 따라야 합니다. 따라서 B=A'B입니다. NAND 게이트를 사용하는 반감기NAND 게이트 및 NOR 게이트를 유니버설 게이트라고 합니다. 여기서 NAND 게이트는 n개의 NAND 게이트 조합을 사용하여 모든 유형의 디지털 회로를 설계할 수 있기 때문에 범용 게이트라고 합니다. 이러한 특성으로 인해 NAND 게이트는 범용 게이트라고 불립니다. 이제 NAND 게이트를 사용하여 Half-Subtractor 회로를 설계합니다.

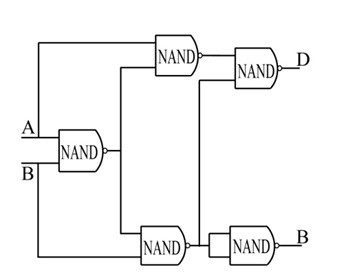

차이(D) 및 배로우(B)에 대한 K-맵에 따르면 첫 번째 함축 항목은 A'B이고 두 번째 함축 항목은 AB'입니다. 이 두 함축 방정식을 단순화하면 DD의 차이에 대한 단순화된 방정식을 얻을 수 있습니다. =A'B+AB'그러면 D=A⊕B입니다. 이 방정식은 단순히 Ex-OR 게이트를 나타냅니다. 배로우 B에 대한 단순화된 부울 표현식을 찾으려면 차이 D에 대해 따랐던 것과 동일한 프로세스를 따라야 합니다. 따라서 B=A'B입니다. NAND 게이트를 사용하는 반감기NAND 게이트 및 NOR 게이트를 유니버설 게이트라고 합니다. 여기서 NAND 게이트는 n개의 NAND 게이트 조합을 사용하여 모든 유형의 디지털 회로를 설계할 수 있기 때문에 범용 게이트라고 합니다. 이러한 특성으로 인해 NAND 게이트는 범용 게이트라고 불립니다. 이제 NAND 게이트를 사용하여 Half-Subtractor 회로를 설계합니다. NAND 게이트로 구현된 반감산기우리는 XNUMX개의 NAND 게이트로 반감기 회로를 설계할 수 있습니다. A와 B를 NAND 게이트의 첫 번째 단계에 대한 입력으로 간주하고 출력은 두 번째 NAND 게이트에 대한 하나의 입력으로 다시 연결됩니다. 뿐만 아니라 세 번째 NAND 게이트. 입력에 따라 출력을 제공하고 NAND 게이트의 최종 단계에서 차이 출력 D와 배로우 출력 B가 출력에 있습니다. 최종 차이 D 출력 방정식은 D = A ⊕B 및 배로우 B 방정식은 B=A'B입니다. 반감산기를 구성하기 위해 NAND 게이트의 다른 조합을 사용함으로써 차이와 배로우의 최종 방정식은 D= A⊕B 및 B=A'B만 됩니다. 이 감산기의 다양한 응용 프로그램이 있습니다. 실제로 그들은 분석하기 쉽습니다. 그 중 일부는 다음과 같이 나열됩니다. 열에서 가장 작은 위치에 있는 숫자를 빼려면 이러한 빼기가 선호됩니다. 프로세서에 있는 ALU(Arithmetic and Logic Unit)는 빼기에 이 단위를 선호합니다. 사운드의 왜곡을 최소화하기 위해 이것들이 사용됩니다. 필요한 작업에 따라 반 감산기는 연산자 수를 늘리거나 줄일 수 있습니다. 반 감산기는 증폭기에 사용됩니다. 오디오 신호를 전송하는 동안 왜곡을 피하기 위해 사용됩니다. 따라서 이것이 전부입니다. 반감산기 회로. 실시간 조건에서는 반감기를 사용하여 여러 비트 수를 뺄 수 없습니다. 이 단점은 전체 감산기를 사용하여 극복할 수 있습니다.

NAND 게이트로 구현된 반감산기우리는 XNUMX개의 NAND 게이트로 반감기 회로를 설계할 수 있습니다. A와 B를 NAND 게이트의 첫 번째 단계에 대한 입력으로 간주하고 출력은 두 번째 NAND 게이트에 대한 하나의 입력으로 다시 연결됩니다. 뿐만 아니라 세 번째 NAND 게이트. 입력에 따라 출력을 제공하고 NAND 게이트의 최종 단계에서 차이 출력 D와 배로우 출력 B가 출력에 있습니다. 최종 차이 D 출력 방정식은 D = A ⊕B 및 배로우 B 방정식은 B=A'B입니다. 반감산기를 구성하기 위해 NAND 게이트의 다른 조합을 사용함으로써 차이와 배로우의 최종 방정식은 D= A⊕B 및 B=A'B만 됩니다. 이 감산기의 다양한 응용 프로그램이 있습니다. 실제로 그들은 분석하기 쉽습니다. 그 중 일부는 다음과 같이 나열됩니다. 열에서 가장 작은 위치에 있는 숫자를 빼려면 이러한 빼기가 선호됩니다. 프로세서에 있는 ALU(Arithmetic and Logic Unit)는 빼기에 이 단위를 선호합니다. 사운드의 왜곡을 최소화하기 위해 이것들이 사용됩니다. 필요한 작업에 따라 반 감산기는 연산자 수를 늘리거나 줄일 수 있습니다. 반 감산기는 증폭기에 사용됩니다. 오디오 신호를 전송하는 동안 왜곡을 피하기 위해 사용됩니다. 따라서 이것이 전부입니다. 반감산기 회로. 실시간 조건에서는 반감기를 사용하여 여러 비트 수를 뺄 수 없습니다. 이 단점은 전체 감산기를 사용하여 극복할 수 있습니다.

메시지를 남겨주세요

메시지 목록

댓글로드 중 ...