제품 카테고리

제품 태그

Fmuser 사이트

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> 아프리칸스어

- sq.fmuser.net -> 알바니아어

- ar.fmuser.net -> 아랍어

- hy.fmuser.net -> 아르메니아어

- az.fmuser.net -> 아제르바이잔 어

- eu.fmuser.net -> 바스크

- be.fmuser.net -> 벨로루시 어

- bg.fmuser.net -> 불가리아어

- ca.fmuser.net -> 카탈로니아 어

- zh-CN.fmuser.net -> 중국어 (간체)

- zh-TW.fmuser.net -> 중국어 (번체)

- hr.fmuser.net -> 크로아티아어

- cs.fmuser.net -> 체코

- da.fmuser.net -> 덴마크어

- nl.fmuser.net -> 네덜란드어

- et.fmuser.net -> 에스토니아어

- tl.fmuser.net -> 필리피노

- fi.fmuser.net -> 핀란드어

- fr.fmuser.net -> 프랑스어

- gl.fmuser.net -> 갈리시아어

- ka.fmuser.net -> 조지아 어

- de.fmuser.net -> 독일어

- el.fmuser.net -> 그리스

- ht.fmuser.net -> 아이티 크리올

- iw.fmuser.net -> 히브리어

- hi.fmuser.net -> 힌디어

- hu.fmuser.net 헝가리어

- is.fmuser.net -> 아이슬란드 어

- id.fmuser.net -> 인도네시아어

- ga.fmuser.net -> 아일랜드어

- it.fmuser.net -> 이탈리아어

- ja.fmuser.net -> 일본어

- ko.fmuser.net -> 한국어

- lv.fmuser.net -> 라트비아어

- lt.fmuser.net 리투아니아어

- mk.fmuser.net -> 마케도니아 어

- ms.fmuser.net -> 말레이어

- mt.fmuser.net -> 몰타어

- no.fmuser.net -> 노르웨이어

- fa.fmuser.net -> 페르시아어

- pl.fmuser.net -> 폴란드어

- pt.fmuser.net -> 포르투갈어

- ro.fmuser.net -> 루마니아어

- ru.fmuser.net -> 러시아어

- sr.fmuser.net -> 세르비아어

- sk.fmuser.net -> 슬로바키아어

- sl.fmuser.net -> 슬로베니아어

- es.fmuser.net -> 스페인어

- sw.fmuser.net -> 스와힐리

- sv.fmuser.net -> 스웨덴어

- th.fmuser.net -> 태국

- tr.fmuser.net -> 터키어

- uk.fmuser.net -> 우크라이나어

- ur.fmuser.net -> 우르두어

- vi.fmuser.net -> 베트남어

- cy.fmuser.net -> 웨일스 어

- yi.fmuser.net -> 이디시어

Half Adder 란 무엇입니까 : 회로도 및 응용

Date:2021/10/18 21:55:58 Hits:

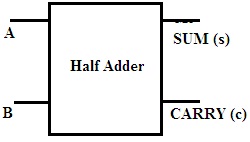

Half Adder는 일종의 기본 디지털 회로입니다. 이전에는 아날로그 회로에서 다양한 작업이 수행되었습니다. 디지털 전자 장치가 발견 된 후 유사한 작업이 수행됩니다. 디지털 시스템은 효과적이고 신뢰할 수 있는 것으로 간주됩니다. 다양한 연산 중에서 가장 눈에 띄는 연산 중 하나는 산술 연산입니다. 여기에는 더하기, 빼기, 곱하기 및 나누기가 포함됩니다. 그러나 그것이 컴퓨터일 수 있다는 것은 이미 알려져 있으며 계산기와 같은 전자 장치는 수학 연산을 수행할 수 있습니다. 이러한 작업은 이진 값으로 구성됩니다.이것은 특정 회로가 있어야 가능합니다. 이러한 회로를 이진 가산기 및 감산기라고 합니다. 이 유형의 회로는 바이너리 코드, Excess-3 코드 및 기타 코드용으로 설계되었습니다. 추가 이진 가산기는 두 가지 유형으로 분류됩니다. 반가산기 및 전가산기 반가산기란 무엇입니까? 이진수에 덧셈을 수행하는 기능을 하는 디지털 전자 회로를 반가산기라고 합니다. 덧셈의 과정은 denary이며 유일한 차이점은 선택된 숫자 체계입니다. 이진법에는 0과 1만 존재한다. 숫자의 가중치는 완전히 이진수의 위치를 기반으로 합니다. 1과 0 중 1은 가장 큰 숫자로, 0은 작은 숫자로 처리됩니다. 이 가산기의 블록다이어그램은 Half AdderHalf Adder 회로도 Half Adder는 XNUMX개의 입력으로 구성되어 XNUMX개의 출력을 생성합니다. 가장 단순한 디지털 회로로 간주됩니다. 이 회로에 대한 입력은 추가가 수행될 비트입니다. 얻은 출력은 합계와 캐리입니다.

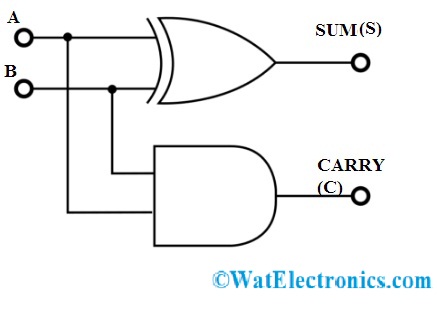

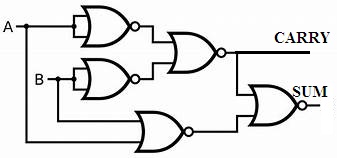

Half AdderHalf Adder 회로도 Half Adder는 XNUMX개의 입력으로 구성되어 XNUMX개의 출력을 생성합니다. 가장 단순한 디지털 회로로 간주됩니다. 이 회로에 대한 입력은 추가가 수행될 비트입니다. 얻은 출력은 합계와 캐리입니다.  Half Adder 이 가산기의 회로는 두 개의 게이트로 구성됩니다. AND 및 XOR 게이트입니다. 적용된 입력은 회로에 있는 두 게이트 모두에 대해 동일합니다. 그러나 출력은 각 게이트에서 가져옵니다. XOR 게이트의 출력은 SUM이라고 하고 AND의 출력은 CARRY로 알려져 있습니다. 반가산기 진리표 적용된 입력에 대해 얻은 출력의 관계를 얻으려면 진리표라고 하는 테이블을 사용하여 분석할 수 있습니다.

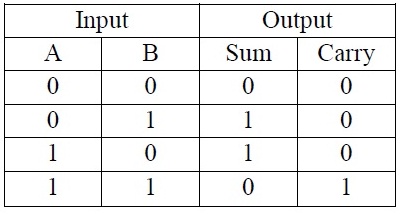

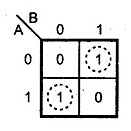

Half Adder 이 가산기의 회로는 두 개의 게이트로 구성됩니다. AND 및 XOR 게이트입니다. 적용된 입력은 회로에 있는 두 게이트 모두에 대해 동일합니다. 그러나 출력은 각 게이트에서 가져옵니다. XOR 게이트의 출력은 SUM이라고 하고 AND의 출력은 CARRY로 알려져 있습니다. 반가산기 진리표 적용된 입력에 대해 얻은 출력의 관계를 얻으려면 진리표라고 하는 테이블을 사용하여 분석할 수 있습니다. 반가산기 진리표 위의 진리표에서 요점은 다음과 같이 분명합니다. A=0인 경우 B=0이 적용된 입력은 모두 0입니다. 그러면 출력 SUM과 CARRY는 모두 0입니다. 입력이 1이면 SUM은 e1이지만 CARRY는 0입니다. 두 입력이 모두 1이면 SUM은 0과 같고 CARRY는 1과 같습니다. 적용된 입력을 기반으로 반가산기가 작업을 진행합니다. 덧셈의 방정식 이러한 유형의 회로에 대한 방정식은 SOP(Sum of Products) 및 POS(Products of Sum) 개념으로 실현할 수 있습니다. 이러한 유형의 회로에 대한 부울 방정식은 적용된 입력과 획득된 출력 간의 관계를 결정합니다. 방정식을 결정하기 위해 k-맵은 진리표 값을 기반으로 그려집니다. 두 개의 논리 게이트가 사용되기 때문에 두 개의 방정식으로 구성됩니다. 캐리의 k-맵은 다음과 같습니다.

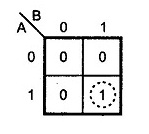

반가산기 진리표 위의 진리표에서 요점은 다음과 같이 분명합니다. A=0인 경우 B=0이 적용된 입력은 모두 0입니다. 그러면 출력 SUM과 CARRY는 모두 0입니다. 입력이 1이면 SUM은 e1이지만 CARRY는 0입니다. 두 입력이 모두 1이면 SUM은 0과 같고 CARRY는 1과 같습니다. 적용된 입력을 기반으로 반가산기가 작업을 진행합니다. 덧셈의 방정식 이러한 유형의 회로에 대한 방정식은 SOP(Sum of Products) 및 POS(Products of Sum) 개념으로 실현할 수 있습니다. 이러한 유형의 회로에 대한 부울 방정식은 적용된 입력과 획득된 출력 간의 관계를 결정합니다. 방정식을 결정하기 위해 k-맵은 진리표 값을 기반으로 그려집니다. 두 개의 논리 게이트가 사용되기 때문에 두 개의 방정식으로 구성됩니다. 캐리의 k-맵은 다음과 같습니다.  K-Map AND 게이트 CARRY의 출력 방정식은 AND 게이트에서 얻습니다.C=A.BSUM에 대한 부울 표현식은 SOP 형식으로 구현됩니다. 따라서 SUM에 대한 K-맵은 다음과 같습니다.

K-Map AND 게이트 CARRY의 출력 방정식은 AND 게이트에서 얻습니다.C=A.BSUM에 대한 부울 표현식은 SOP 형식으로 구현됩니다. 따라서 SUM에 대한 K-맵은 다음과 같습니다. K-Map for Sum(XOR) 결정된 방정식은 S= A⊕ B응용 이 기본 가산기의 응용은 다음과 같습니다. 이진 비트에 덧셈을 수행하려면 컴퓨터에 있는 산술 및 논리 장치가 이 가산기 회로를 선호합니다. 전가산기 회로의 형성. 이 논리 회로는 계산기 설계에서 선호됩니다. 주소와 테이블을 계산하려면 이러한 회로가 선호됩니다. 이 회로는 덧셈 대신 디지털 회로의 다양한 응용 프로그램을 처리할 수 있습니다. 또한 이것은 디지털 전자 장치의 핵심이 됩니다.VHDL 코드반가산기 회로에 대한 VHDL 코드는 라이브러리 islibrary ieee;use ieee.std_logic_1164.all;entity half_adder isport(a,b: in bit; sum,carry:out bit);end half_adder ;half_adder의 아키텍처 데이터 isbeginsum<= a xor b;carry <= a 및 b;end data;FAQs1. 가산기란 무엇을 의미합니까? 가산기를 수행하는 것이 유일한 목적인 디지털 회로를 가산기라고 합니다. 이들은 ALU의 주요 구성 요소입니다. 가산기는 다양한 형식의 숫자 외에도 작동합니다. 가산기의 출력은 sum과 carry.2입니다. Half Adder의 한계는 무엇입니까? 이전 비트에서 생성된 캐리 비트는 추가할 수 없다는 것이 이 Adder의 한계입니다. 다중 비트에 대한 추가를 수행하려면 이러한 회로를 선호할 수 없습니다.3. NOR 게이트를 사용하여 반가산기를 구현하는 방법?이 유형의 가산기 구현은 NOR 게이트를 사용하여 수행할 수도 있습니다. 이것은 또 다른 유니버설 게이트입니다.

K-Map for Sum(XOR) 결정된 방정식은 S= A⊕ B응용 이 기본 가산기의 응용은 다음과 같습니다. 이진 비트에 덧셈을 수행하려면 컴퓨터에 있는 산술 및 논리 장치가 이 가산기 회로를 선호합니다. 전가산기 회로의 형성. 이 논리 회로는 계산기 설계에서 선호됩니다. 주소와 테이블을 계산하려면 이러한 회로가 선호됩니다. 이 회로는 덧셈 대신 디지털 회로의 다양한 응용 프로그램을 처리할 수 있습니다. 또한 이것은 디지털 전자 장치의 핵심이 됩니다.VHDL 코드반가산기 회로에 대한 VHDL 코드는 라이브러리 islibrary ieee;use ieee.std_logic_1164.all;entity half_adder isport(a,b: in bit; sum,carry:out bit);end half_adder ;half_adder의 아키텍처 데이터 isbeginsum<= a xor b;carry <= a 및 b;end data;FAQs1. 가산기란 무엇을 의미합니까? 가산기를 수행하는 것이 유일한 목적인 디지털 회로를 가산기라고 합니다. 이들은 ALU의 주요 구성 요소입니다. 가산기는 다양한 형식의 숫자 외에도 작동합니다. 가산기의 출력은 sum과 carry.2입니다. Half Adder의 한계는 무엇입니까? 이전 비트에서 생성된 캐리 비트는 추가할 수 없다는 것이 이 Adder의 한계입니다. 다중 비트에 대한 추가를 수행하려면 이러한 회로를 선호할 수 없습니다.3. NOR 게이트를 사용하여 반가산기를 구현하는 방법?이 유형의 가산기 구현은 NOR 게이트를 사용하여 수행할 수도 있습니다. 이것은 또 다른 유니버설 게이트입니다. NOR gates4를 사용하는 반가산기. NAND 게이트를 사용하여 Half Adder를 구현하는 방법? NAND 게이트는 범용 게이트의 일종입니다. NAND 게이트를 이용하면 어떤 회로 설계도 가능함을 나타낸다.

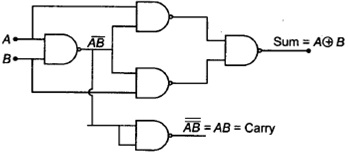

NOR gates4를 사용하는 반가산기. NAND 게이트를 사용하여 Half Adder를 구현하는 방법? NAND 게이트는 범용 게이트의 일종입니다. NAND 게이트를 이용하면 어떤 회로 설계도 가능함을 나타낸다. Half Adder 위의 회로에서 한 NAND 게이트의 출력을 입력에 다른 NAND 게이트로 적용하여 캐리 출력을 생성할 수 있습니다. 그것은 AND 게이트에서 얻은 출력에 익숙할 뿐입니다. SUM의 출력 방정식은 A 및 B의 개별 입력과 함께 초기 NAND 게이트의 출력을 추가 NAND 게이트에 적용하여 생성할 수 있습니다. 마지막으로, 해당 NAND 게이트에서 얻은 출력이 게이트에 다시 적용됩니다. 따라서 SUM에 대한 출력이 생성됩니다. 따라서 디지털 회로의 기본 가산기는 다양한 논리 게이트를 사용하여 설계할 수 있습니다. 그러나 다중 비트 덧셈은 복잡해지고 반가산기의 한계로 여겨진다. 실제 카운터에서 증가 작업에 사용되는 IC를 설명할 수 있습니까?

Half Adder 위의 회로에서 한 NAND 게이트의 출력을 입력에 다른 NAND 게이트로 적용하여 캐리 출력을 생성할 수 있습니다. 그것은 AND 게이트에서 얻은 출력에 익숙할 뿐입니다. SUM의 출력 방정식은 A 및 B의 개별 입력과 함께 초기 NAND 게이트의 출력을 추가 NAND 게이트에 적용하여 생성할 수 있습니다. 마지막으로, 해당 NAND 게이트에서 얻은 출력이 게이트에 다시 적용됩니다. 따라서 SUM에 대한 출력이 생성됩니다. 따라서 디지털 회로의 기본 가산기는 다양한 논리 게이트를 사용하여 설계할 수 있습니다. 그러나 다중 비트 덧셈은 복잡해지고 반가산기의 한계로 여겨진다. 실제 카운터에서 증가 작업에 사용되는 IC를 설명할 수 있습니까?

메시지를 남겨주세요

메시지 목록

댓글로드 중 ...