제품 카테고리

제품 태그

Fmuser 사이트

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> 아프리칸스어

- sq.fmuser.net -> 알바니아어

- ar.fmuser.net -> 아랍어

- hy.fmuser.net -> 아르메니아어

- az.fmuser.net -> 아제르바이잔 어

- eu.fmuser.net -> 바스크

- be.fmuser.net -> 벨로루시 어

- bg.fmuser.net -> 불가리아어

- ca.fmuser.net -> 카탈로니아 어

- zh-CN.fmuser.net -> 중국어 (간체)

- zh-TW.fmuser.net -> 중국어 (번체)

- hr.fmuser.net -> 크로아티아어

- cs.fmuser.net -> 체코

- da.fmuser.net -> 덴마크어

- nl.fmuser.net -> 네덜란드어

- et.fmuser.net -> 에스토니아어

- tl.fmuser.net -> 필리피노

- fi.fmuser.net -> 핀란드어

- fr.fmuser.net -> 프랑스어

- gl.fmuser.net -> 갈리시아어

- ka.fmuser.net -> 조지아 어

- de.fmuser.net -> 독일어

- el.fmuser.net -> 그리스

- ht.fmuser.net -> 아이티 크리올

- iw.fmuser.net -> 히브리어

- hi.fmuser.net -> 힌디어

- hu.fmuser.net 헝가리어

- is.fmuser.net -> 아이슬란드 어

- id.fmuser.net -> 인도네시아어

- ga.fmuser.net -> 아일랜드어

- it.fmuser.net -> 이탈리아어

- ja.fmuser.net -> 일본어

- ko.fmuser.net -> 한국어

- lv.fmuser.net -> 라트비아어

- lt.fmuser.net 리투아니아어

- mk.fmuser.net -> 마케도니아 어

- ms.fmuser.net -> 말레이어

- mt.fmuser.net -> 몰타어

- no.fmuser.net -> 노르웨이어

- fa.fmuser.net -> 페르시아어

- pl.fmuser.net -> 폴란드어

- pt.fmuser.net -> 포르투갈어

- ro.fmuser.net -> 루마니아어

- ru.fmuser.net -> 러시아어

- sr.fmuser.net -> 세르비아어

- sk.fmuser.net -> 슬로바키아어

- sl.fmuser.net -> 슬로베니아어

- es.fmuser.net -> 스페인어

- sw.fmuser.net -> 스와힐리

- sv.fmuser.net -> 스웨덴어

- th.fmuser.net -> 태국

- tr.fmuser.net -> 터키어

- uk.fmuser.net -> 우크라이나어

- ur.fmuser.net -> 우르두어

- vi.fmuser.net -> 베트남어

- cy.fmuser.net -> 웨일스 어

- yi.fmuser.net -> 이디시어

PMOS 및 NMOS 트랜지스터

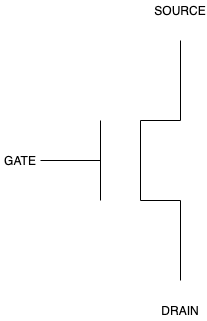

마이크로프로세서는 트랜지스터로 구성됩니다. 특히, MOS 트랜지스터로 구성됩니다. MOS는 Metal-Oxide Semiconductor의 약자입니다. MOS 트랜지스터에는 pMOS(포지티브 MOS)와 nMOS(네거티브 MOS)의 두 가지 유형이 있습니다. 모든 pMOS 및 nMOS에는 게이트, 소스 및 드레인의 세 가지 주요 구성 요소가 장착되어 있습니다.

pMOS와 nMOS가 어떻게 작동하는지 제대로 이해하려면 먼저 몇 가지 용어를 정의하는 것이 중요합니다.

폐쇄 회로: 이것은 전기가 게이트에서 소스로 흐르고 있음을 의미합니다.

개방 회로: 이것은 전기가 게이트에서 소스로 흐르지 않는다는 것을 의미합니다. 오히려 게이트에서 드레인으로 전기가 흐르고 있습니다.

nMOS 트랜지스터가 무시할 수 없는 전압을 수신하면 소스에서 드레인으로의 연결이 와이어처럼 작동합니다. 전기는 제한 없이 소스에서 드레인으로 흐를 것입니다. 이것을 폐쇄 회로라고 합니다. 반면에, nMOS 트랜지스터가 약 0볼트의 전압을 수신하면 소스에서 드레인으로의 연결이 끊어지며 이것을 개방 회로라고 합니다.

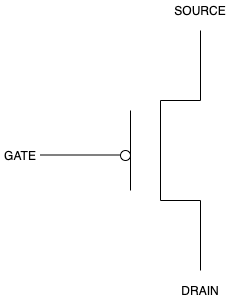

p형 트랜지스터는 n형 트랜지스터와 정확히 반대로 작동합니다. nMOS는 전압이 무시할 수 없을 때 소스와 폐쇄 회로를 형성하는 반면, pMOS는 전압이 무시할 수 없을 때 소스와 개방 회로를 형성합니다.

위에 표시된 pMOS 트랜지스터의 이미지에서 볼 수 있듯이 pMOS 트랜지스터와 nMOS 트랜지스터의 유일한 차이점은 게이트와 첫 번째 막대 사이의 작은 원입니다. 이 원은 전압에서 값을 반전시킵니다. 따라서 게이트가 1 값을 나타내는 전압을 보내면 인버터는 1을 0으로 변경하고 회로가 그에 따라 작동하도록 합니다.

pMOS와 nMOS는 반대 방식으로(상보적 방식으로) 기능하기 때문에 이 둘을 하나의 거대한 MOS 회로로 결합하면 상보성 금속 산화물 반도체를 나타내는 cMOS 회로라고 합니다.

MOS 회로 활용

pMOS와 nMOS 회로를 결합하여 GATES라고 하는 보다 복잡한 구조, 보다 구체적으로 논리 게이트를 구축할 수 있습니다. 우리는 이미 이전 블로그에서 이러한 논리 함수의 개념과 관련 진리표를 소개했습니다. 여기에서 지금 확인해 보세요..

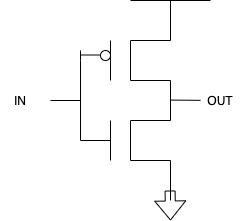

소스에 연결하는 pMOS 트랜지스터와 접지에 연결하는 nMOS 트랜지스터를 연결할 수 있습니다. 이것은 CMOS 트랜지스터의 첫 번째 예가 될 것입니다.

이 cMOS 트랜지스터는 NOT 논리 함수와 유사한 방식으로 작동합니다.

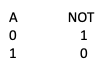

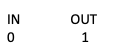

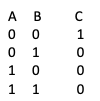

NOT 진리표를 살펴보겠습니다.

NOT 진리표에서 모든 입력 값: A는 반전됩니다. 위의 회로는 어떻게 될까요?

입력이 0이라고 가정해 보겠습니다.

0은 pMOS(상단)와 nMOS(하단) 모두에 연결되어 위아래로 움직입니다. 값 0이 pMOS에 도달하면 1로 반전됩니다. 따라서 소스에 대한 연결이 닫힙니다. 이것은 접지(드레인)에 대한 연결도 닫히지 않는 한 논리 값 1을 생성합니다. 음, 트랜지스터는 상보적이기 때문에 nMOS 트랜지스터가 값을 반전시키지 않는다는 것을 압니다. 따라서 값 0을 그대로 사용하므로 접지(드레인)에 개방 회로를 생성합니다. 따라서 게이트에 대해 논리값 1이 생성됩니다.

IN 값이 1이면 어떻게 됩니까? 음, 위와 동일한 단계를 따르면 값 1이 pMOS와 nMOS 모두에 전송됩니다. 값이 pMOS에 의해 수신되면 값은 0으로 반전됩니다. 따라서 SOURCE에 대한 연결이 열려 있습니다. 값이 nMOS에 수신되면 값이 반전되지 않습니다. 따라서 값은 1로 유지됩니다. nMOS에서 값 1을 수신하면 연결이 닫힙니다. 따라서 접지와의 연결이 닫힙니다. 이것은 논리값 0을 생성합니다.

두 세트의 입력/출력을 합치면 다음이 생성됩니다.

이 진리표가 논리 함수 NOT이 생성하는 것과 정확히 동일하다는 것을 보는 것은 매우 쉽습니다. 따라서 이것은 NOT 게이트로 알려져 있습니다.

이 두 개의 간단한 트랜지스터를 사용하여 더 복잡한 구조를 만들 수 있습니까? 전적으로! 다음으로 우리는 NOR 게이트와 OR 게이트를 만들 것입니다.

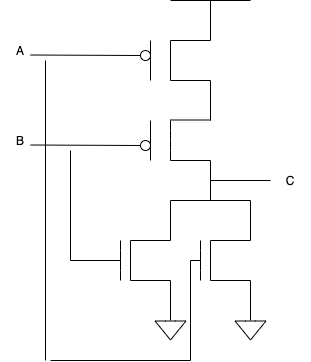

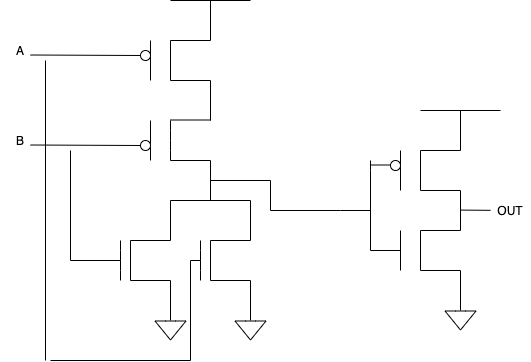

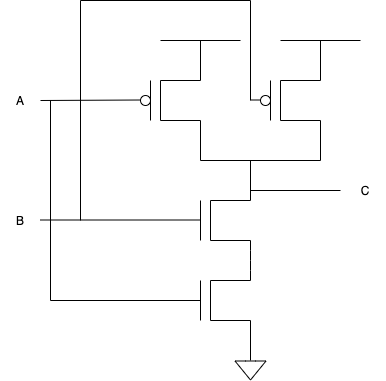

이 회로는 상단에 XNUMX개의 pMOS 트랜지스터를 사용하고 하단에 XNUMX개의 nMOS 트랜지스터를 사용합니다. 다시 게이트에 대한 입력을 살펴보고 어떻게 동작하는지 살펴보겠습니다.

A가 0이고 B가 0일 때 이 게이트는 pMOS 트랜지스터에 도달할 때 두 값을 모두 1로 반전시킵니다. 그러나 nMOS 트랜지스터는 둘 다 0의 값을 유지합니다. 그러면 게이트가 1의 값을 생성합니다.

A가 0이고 B가 1일 때 이 게이트는 pMOS 트랜지스터에 도달할 때 두 값을 모두 반전시킵니다. 따라서 A는 1로 변경되고 B는 0으로 변경됩니다. 이것은 소스로 이어지지 않습니다. 두 트랜지스터 모두 입력을 소스에 연결하기 위해 폐쇄 회로가 필요하기 때문입니다. nMOS 트랜지스터는 값을 반전하지 않습니다. 따라서 A와 관련된 nMOS는 0을 생성하고 B와 관련된 nMOS는 1을 생성합니다. 따라서 B와 관련된 nMOS는 접지에 대한 폐쇄 회로를 생성합니다. 그러면 게이트가 0 값을 생성합니다.

A가 1이고 B가 0일 때 이 게이트는 pMOS 트랜지스터에 도달할 때 두 값을 모두 반전시킵니다. 따라서 A는 0으로 변경되고 B는 1로 변경됩니다. 이것은 소스로 이어지지 않습니다. 두 트랜지스터 모두 입력을 소스에 연결하기 위해 폐쇄 회로가 필요하기 때문입니다. nMOS 트랜지스터는 값을 반전시키지 않습니다. 따라서 A와 관련된 nMOS는 1을 생성하고 B와 관련된 nMOS는 0을 생성합니다. 따라서 A와 관련된 nMOS는 접지에 대해 폐쇄 회로를 생성합니다. 그러면 게이트가 0 값을 생성합니다.

A가 1이고 B가 1일 때 이 게이트는 pMOS 트랜지스터에 도달할 때 두 값을 모두 반전시킵니다. 따라서 A는 0으로 변경되고 B는 0으로 변경됩니다. 이것은 소스로 이어지지 않습니다. 두 트랜지스터 모두 입력을 소스에 연결하기 위해 폐쇄 회로가 필요하기 때문입니다. nMOS 트랜지스터는 값을 반전하지 않습니다. 따라서 A와 관련된 nMOS는 1을 생성하고 B와 관련된 nMOS는 1을 생성합니다. 따라서 A와 관련된 nMOS 및 B와 관련된 nMOS는 접지에 대한 폐쇄 회로를 생성합니다. 그러면 게이트가 0 값을 생성합니다.

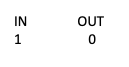

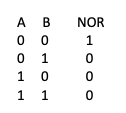

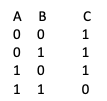

따라서 게이트의 진리표는 다음과 같습니다.

한편, NOR 논리 함수의 진리표는 다음과 같습니다.

따라서 이 게이트가 NOR 논리 함수와 진리표를 공유하기 때문에 이 게이트가 NOR 게이트임을 확인했습니다.

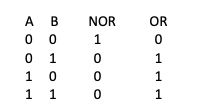

이제 지금까지 만든 두 개의 게이트를 합쳐 OR 게이트를 만들어 보겠습니다. NOR는 NOT OR을 나타냅니다. 따라서 이미 뒤집힌 게이트를 뒤집으면 원래대로 돌아갑니다. 실제로 작동하는지 확인하기 위해 이것을 테스트해 보겠습니다.

여기서 우리가 한 것은 이전의 NOR 게이트를 가져와서 출력에 NOT 게이트를 적용한 것입니다. 위에서 보았듯이 NOT 게이트는 값 1을 취하여 0을 출력하고 NOT 게이트는 값 0을 취하여 1을 출력합니다.

이것은 NOR 게이트의 값을 취하고 모든 0을 1로, 1을 0으로 변환합니다. 따라서 진리표는 다음과 같습니다.

이 게이트를 테스트하는 연습을 더 하고 싶다면 위의 값을 직접 시도해보고 게이트가 동일한 결과를 생성하는지 확인하십시오!

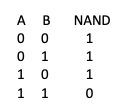

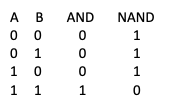

나는 이것이 NAND 게이트라고 주장하지만, 이 게이트의 진리표를 테스트하여 이것이 정말로 NAND 게이트인지 확인해보자.

A가 0이고 B가 0일 때 A의 pMOS는 1을 생성하고 A의 nMOS는 0을 생성합니다. 따라서 이 게이트는 폐쇄 회로로 소스에 연결되고 개방 회로로 접지에서 분리되기 때문에 논리 1을 생성합니다.

A가 0이고 B가 1일 때 A의 pMOS는 1을 생성하고 A의 nMOS는 0을 생성합니다. 따라서 이 게이트는 폐쇄 회로로 소스에 연결되고 개방 회로로 접지에서 분리되기 때문에 논리 1을 생성합니다.

A가 1이고 B가 0일 때 B의 pMOS는 1을 생성하고 B의 nMOS는 0을 생성합니다. 따라서 이 게이트는 폐쇄 회로로 소스에 연결되고 개방 회로로 접지에서 분리되기 때문에 논리 1을 생성합니다.

A가 1이고 B가 1일 때 A의 pMOS는 0을 생성하고 A의 nMOS는 1을 생성합니다. 따라서 B의 pMOS와 nMOS도 확인해야 합니다. B의 pMOS는 0을 생성하고 B의 nMOS는 1을 생성합니다. 따라서 이 게이트는 개방 회로로 소스에서 분리되고 폐쇄 회로로 접지에 연결되기 때문에 논리 0을 생성합니다.

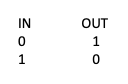

진리표는 다음과 같습니다.

한편, NAND 논리 함수의 진리표는 다음과 같습니다.

따라서 우리는 이것이 실제로 NAND 게이트임을 확인했습니다.

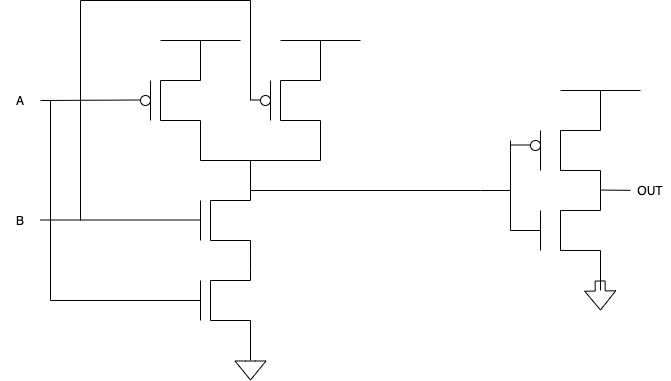

이제 AND 게이트를 어떻게 만들까요? 글쎄, 우리는 NOR 게이트에서 OR 게이트를 만든 것과 똑같은 방식으로 AND 게이트를 만들 것이다! 인버터를 부착해 드립니다!

우리가 한 일은 NAND 게이트의 출력에 NOT 함수를 적용한 것뿐이므로 진리표는 다음과 같습니다.

다시한번 제가 말씀드리는 내용이 사실인지 확인 부탁드립니다.

오늘, 우리는 pMOS와 nMOS 트랜지스터가 무엇인지, 그리고 그것들을 사용하여 더 복잡한 구조를 만드는 방법을 다루었습니다! 이 블로그가 유익한 정보였기를 바랍니다. 내 이전 블로그를 읽고 싶다면 아래 목록을 찾을 수 있습니다.